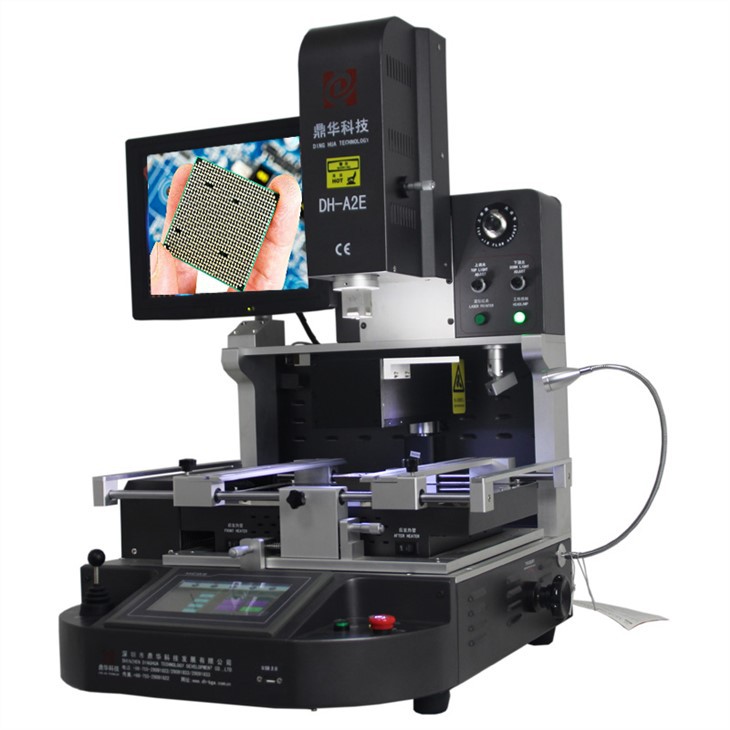

Stesen Kerja Semula BGA Optik Auto

Digunakan secara meluas dalam pembaikan peringkat cip untuk papan induk mudah alih, komputer riba, komputer, TV, penghawa dingin dan lain-lain. Ia mempunyai kadar kejayaan pembaikan yang tinggi dan tahap automasi yang tinggi dan menjimatkan banyak usaha manusia. Kami adalah pengilang profesional mesin ini dan mempunyai mesin ini tersedia dalam stok.

Description/kawalan

Stesen Kerja Semula BGA Optik Auto

1.Aplikasi Stesen Kerja Semula BGA Optik Auto

Papan induk komputer, telefon pintar, komputer riba, papan logik MacBook, kamera digital, penghawa dingin, TV dan elektronik lain

peralatan dari industri perubatan, industri komunikasi, industri automobil, dll.

Sesuai untuk pelbagai jenis cip: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, cip LED.

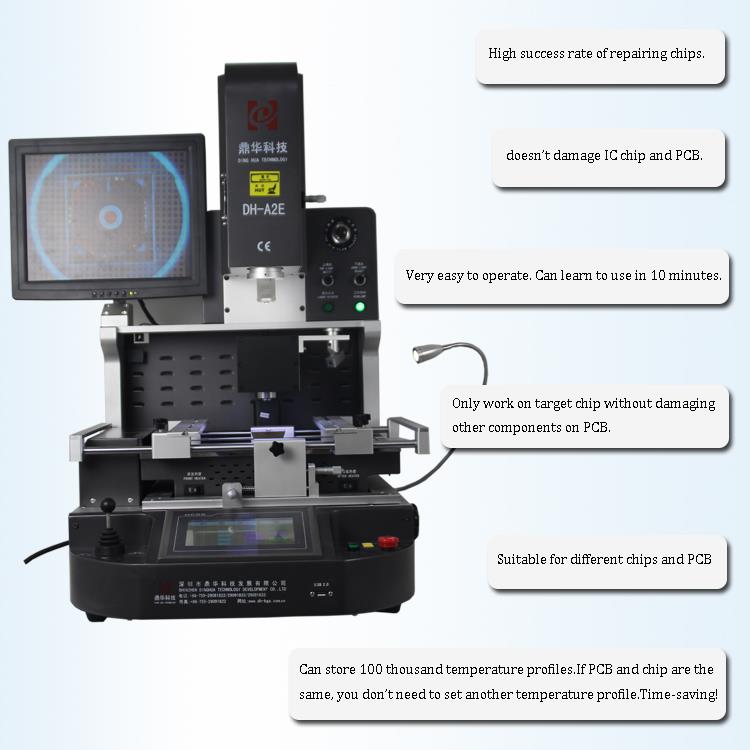

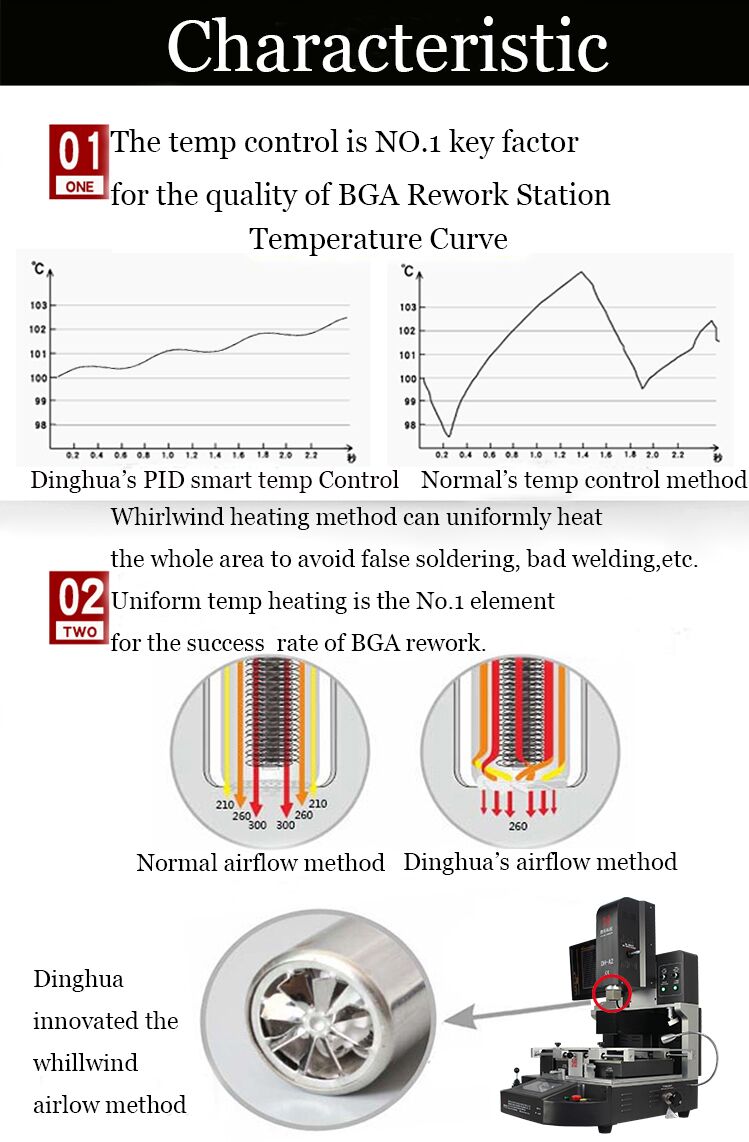

2. Ciri-ciri Produk Stesen Kerja Semula BGA Optik Auto

•Kadar pembaikan tahap cip yang tinggi. Proses penyamarataan, pemasangan dan pematerian adalah automatik.

• Penjajaran tepat setiap sambungan pematerian boleh dijamin dengan kamera CCD penjajaran optik.

•Kawalan suhu yang tepat boleh dipastikan dengan 3 kawasan pemanasan bebas. Mesin boleh set dan simpan

1 juta profil suhu.

• Vakum terbina dalam dalam kepala pelekap mengambil cip BGA secara automatik selepas penyamarataan selesai.

3.Spesifikasi Stesen Kerja Semula BGA Optik Auto

4.Butiran Stesen Kerja Semula BGA Optik Auto

kamera CCD (sistem penjajaran optik yang tepat); 2. paparan digital HD; 3. Mikrometer (laraskan sudut cip);

4.3 pemanas bebas (udara panas & inframerah); 5. Kedudukan laser; 6. Antara muka skrin sentuh HD, kawalan PLC;

7. Led headlamp; 8. Kawalan kayu bedik .

5. Mengapa Memilih Stesen Kerja Semula BGA Optik Auto Kami?

6. Sijil Auto Optical BGA Rework Station

7. Pembungkusan & Penghantaran Stesen Kerja Semula BGA Optik Auto

8.Soalan Lazim

Bagaimana untuk menguji cip?

Ujian cip peringkat sistem awal

SoC adalah berdasarkan proses submikron dalam, jadi menguji peranti Soc baharu memerlukan pendekatan baharu sepenuhnya. Kerana setiap komponen berfungsi

mempunyai keperluan ujian sendiri, jurutera reka bentuk mesti membuat rancangan ujian awal dalam proses reka bentuk.

Pelan ujian blok demi blok untuk peranti SoC mesti dilaksanakan: alat ATPG yang dikonfigurasikan dengan betul untuk ujian logik; masa ujian yang singkat; baru berkelajuan tinggi

model kerosakan dan memori berbilang atau ujian tatasusunan kecil. Untuk barisan pengeluaran, kaedah diagnostik bukan sahaja mencari kesalahan, tetapi juga memisahkan

nod rosak daripada nod kerja. Di samping itu, teknik pemultipleksan ujian harus digunakan apabila mungkin untuk menjimatkan masa ujian. Dalam bidang sangat

ujian IC bersepadu, teknik reka bentuk boleh diuji ATPG dan IDDQ mempunyai mekanisme pemisahan kerosakan yang berkuasa.

Parameter sebenar lain yang perlu dirancang terlebih dahulu termasuk bilangan pin yang perlu diimbas dan jumlah memori pada setiap hujung pin.

Imbasan sempadan boleh dibenamkan pada SoC, tetapi tidak terhad kepada ujian antara sambungan pada papan atau modul berbilang cip.

Walaupun saiz cip semakin berkurangan, cip masih boleh membungkus berjuta-juta hingga 100 juta transistor, dan bilangan mod ujian telah meningkat kepada tidak pernah berlaku sebelum ini.

tahap, menghasilkan kitaran ujian yang lebih panjang. Masalah ini boleh diuji. Mod mampatan untuk menyelesaikan, nisbah mampatan boleh mencapai 20 peratus hingga 60 peratus. Untuk skala besar hari ini

reka bentuk cip, untuk mengelakkan masalah kapasiti, adalah perlu untuk mencari perisian ujian yang boleh dijalankan pada 64-sistem pengendalian bit.

Di samping itu, perisian ujian berhadapan dengan masalah ujian baharu yang disebabkan oleh proses sub-mikron yang mendalam dan kekerapan yang meningkat. Pada masa lalu, mod ujian ATPG untuk

menguji kesalahan menyekat statik tidak lagi terpakai. Menambah corak berfungsi pada alatan tradisional menyukarkan untuk mencari kerosakan baharu. Pendekatan yang lebih baik ialah

kelaskan kumpulan mod kefungsian lalu untuk menentukan ralat yang tidak dapat dikesan, dan kemudian buat mod ATPG untuk menangkap jenis ralat yang hilang ini.

Apabila kapasiti reka bentuk meningkat dan masa ujian setiap transistor berkurangan, untuk mencari masalah berkaitan kelajuan dan mengesahkan pemasaan litar, kaedah ujian segerak

mesti diambil bekerja. Ujian segerak mesti menggabungkan berbilang model kerosakan, termasuk model sementara, kelewatan laluan dan IDDQ.

Sesetengah syarikat dalam industri percaya bahawa menggabungkan kesilapan menyekat, berfungsi dan sementara/laluan kelewatan mungkin merupakan strategi ujian yang paling berkesan. Untuk mendalam

cip submikron dan operasi frekuensi tinggi, ujian kelewatan sementara dan laluan adalah lebih penting.

Untuk menyelesaikan masalah ketepatan ATE apabila menyegerakkan teras ujian dan mengurangkan kos, adalah perlu untuk mencari kaedah baharu yang memudahkan antara muka

peranti ujian (ujian kelewatan sementara dan laluan memerlukan jam yang tepat pada antara muka peranti ujian), Ia memastikan bahawa isyarat cukup tepat semasa ujian.

Memandangkan terdapat kemungkinan besar kecacatan pembuatan dalam blok memori SoC, BIST memori mesti mempunyai fungsi diagnostik. Sebaik sahaja masalah ditemui,

unit alamat yang rosak boleh dipetakan ke memori berlebihan unit alamat ganti, dan alamat kerosakan yang dikesan akan dibuang. Elakkan membuang

keseluruhan cip mahal.

Menguji blok memori terbenam kecil menghapuskan keperluan untuk gerbang tambahan atau logik kawalan. Sebagai contoh, teknik ujian penukaran vektor boleh menukar

mod berfungsi ke dalam satu siri mod imbasan.

Tidak seperti kaedah BIST, input berfungsi blok memori pintasan tidak memerlukan logik tambahan. Kerana tiada logik ujian tambahan diperlukan, SoC

jurutera pembangunan boleh menggunakan semula corak ujian yang telah dibentuk pada masa lalu.

Alat ATPG lanjutan bukan sahaja menguji makro secara selari tetapi juga menentukan sama ada terdapat konflik, serta memperincikan makro yang boleh diuji secara selari dan yang mana

makro tidak boleh diuji secara selari. Selain itu, makro ini boleh diuji dengan berkesan walaupun jam makro adalah sama dengan jam imbasan (seperti ingatan segerak).

Pada masa ini, tiada titik ujian yang mencukupi pada papan dua sisi yang padat, dan setiap cip kompleks mesti dilengkapi dengan litar imbasan sempadan. Tanpa

imbasan sempadan, carian kecacatan pembuatan peringkat papan agak sukar dan bahkan tidak dapat ditemui. Dengan imbasan sempadan, ujian peringkat papan adalah sangat mudah

dan bebas daripada litar logik dalam cip. Imbasan sempadan juga boleh mengkonfigurasi mod ATPG kepada rantai imbasan cip pada mana-mana peringkat pengeluaran.